Working Document

X3T10 2008D

Revision 0 February 28, 1995

Information Technology - AT Attachment-3 Interface (ATA-3)

This is an internal working document of X3T10, a Technical Committee of Accredited Standards Committee X3. As such, this is not a completed standard and has not been approved. The contents may be modified by the X3T10 Technical Committee. The contents are actively being modified by X3T10. This document is made available for review and comment only.

Permission is granted to members of X3, its technical committees, and their associated task groups to reproduce this document for the purposes of X3 standardization activities without further permission, provided this notice is included. All other rights are reserved. Any commercial or for-profit replication or republication is prohibited.

**ASC X3T10 Technical Editor:**

Peter T. McLean Maxtor Corporation 2190 Miller Drive Longmont, CO 80501-6744 USA

Tel: 303-678 2149 Fax: 303-678 2242

Email: pete\_mclean@maxtor.com

#### **Other Points of Contact:**

X3T10 Chair

John B. Lohmeyer

Symbios Logic,Inc.

X3T10 Vice-Chair

Lawrence J. Lamers

Adaptec, Inc.

1635 Aeroplaza Drive

691 S. Milpitas Blvd.

Colorado Springs, CO 80916

Milpitas, CA 95035

Tel:

719-573-3362

Tel:

408-957-7817

Fax: 719-573-3037 Fax: 408-957-7193 Email: john.lohmeyer@hmpd.com Email: ljlamers@aol.com

X3 Secretariat Lynn Barra Administrator Standards Processing X3 Secretariat 1250 Eye Street, NW Suite 200 Washington, DC 20005

Tel: 202-626-5738 Email: LBARRA@ITIC.NW.DC.US

Fax: 202-638-4922

#### **ATA Reflector**

Internet address for subscription to the ATA reflector: majordomo@dt.wdc.com

Send email to above account and include in BODY of text, on a line by itself the following:

"subscribe ata [your email address]"

Internet address for distribution via ATA reflector: ata@dt.wdc.com

ATA Anonymous FTP Site fission.dt.wdc.com

ATA directory is: "/pub/ata"

X3T10 Bulletin Board 719-574-0424

Document Distribution Global Engineering 15 Inverness Way East Englewood, CO 80112-5704

Tel: 303-792-2181 or 800-854-7179

Fax: 303-792-2192

#### **ABSTRACT**

The draft standard for AT Attachment Interface with Extensions (ATA-2) has been completed, but as the popularity of the interface has increased, its application area has grown outside the originally intended purpose. This draft proposed standard is based upon the AT Attachment Interface with Extensions (ATA-2). This document is a stand alone document, separate from that document. The AT Attachment-3 (ATA-3) standard is intended to broaden the scope and application area and take advantage of the huge installed BIOS (Basic Input/Output System) base, and software.

This standard defines an integrated interface between devices and host processors. It provides a common point of attachment for systems manufacturers, system integrators, and suppliers of intelligent devices.

The proposed ATA-3 standard shall maintain a high degree of compatibility with the AT Attachment with Extensions while providing documentation for new capabilities. This proposed standard is not intended to require changes to presently installed devices or existing software. It is intended that this proposed standard would be used to provide additional capabilities.

The proposed ATA-3 standard involves evolutionary expansion of the draft AT Attachment with Extensions standard to provide additional capabilities. The nature of the proposed project is to insure that the AT Attachment has an upward, highly compatible growth path. This will insure that current investments in AT Attachment are provided with more stability in the face of technological developments. It is likely that any isolated negative impacts would occur in any case through non-standard evolution or revolution.

#### PATENT STATEMENT

CAUTION: The developers of this standard have requested that holder's of patents that may be required for the implementation of the standard, disclose such patents to the publisher. However, neither the developers nor the publisher have undertaken a patent search in order to identify which, if any, patents may apply to this standard.

Maxtor Corporation and IBM Corporation have stated that they may have patents or pending patent applications covering subject matter in this document regarding the Security Mode Feature set. The furnishing of this document does not give you any license to those patents. You should send license inquiries, in writing, to:

Mr. Glenn H. Stevens (303) 678-2300 General Counsel Maxtor Corporation 2190 Miller Drive Longmont, Colorado 80501

Mr. John Lowe (914) 742-6275 Intellectual Property and Licensing Services IBM Corporation 500 Columbus Avenue Thornewood, New York 10594

As of the date of publication of this standard and following calls for the identification of patents that may be required for the implementation of the standard, no other such claims have been made. No further patent search is conducted by the developer or the publisher in respect to any standard it processes. No representation is made or implied that licenses are not required to avoid infringement in the use of this standard.

### DOCUMENT STATUS

#### Revision 0

Initial document. Created from X3T10/948D Revision 2k, the proposed AT Attachment Interface with Extensions (ATA-2) standard, and the following proposed additions:

X3T10/94-053r3 Reset Pulse Duration

X3T10/94-087r3 Security Mode

X3T10/94-154r1 Check Power Mode Enhancement

X3T10/95-144r0 Identify Device DMA

X3T10/95-145r0 Device 1 Only

It is the intent of the editor that any changes that may be made to X3T10/948D by the X3T10 be implemented in this document as well. In addition, the editor has taken the liberty to make improvements as deemed necessary, understanding that the entire document is subject to review and change.

### **Contents** 1 Scope 12 3.2.1 Keywords 14 4.5 Electrical Characteristics 20 5.2.1 CS0- (CHIP SELECT 0)......23 5.2.2 CS1- (CHIP SELECT 1)......23 5.2.3 DA2, DA1, and DA0 (DEVICE ADDRESS)......23 5.2.4 DASP- (Device active, device 1 present)......24 5.2.7 DIOW- (Device I/O write)......24 5.2.8 DMACK- (DMA acknowledge) (Optional)......24 5.2.9 DMARQ (DMA request) (Optional).....24 5.2.11 IOCS16- (Device 16-bit I/O)......25 5.2.12 IORDY (I/O channel ready) (Optional)......25 5.2.13 PDIAG- (Passed diagnostics)......26 6.2 I/O register descriptions 28 6.2.10 Sector Count register 39

| 7.1 Reset response                                                           | 43               |

|------------------------------------------------------------------------------|------------------|

| 7.2 Sector Addressing                                                        | 43               |

| 7.3 Power Management Feature Set                                             | 44               |

| 7.3.1 Power modes                                                            | 45               |

| 7.3.2 Power Management Commands                                              | 45               |

| 7.3.3 Standby timer                                                          | 45               |

| 7.3.4 Idle mode transition                                                   | 45               |

| 7.3.5 Status 46                                                              |                  |

| 7.3.6 Power Mode transitions                                                 | 46               |

| 7.3.7 Interface Capability For Power Modes                                   |                  |

| 7.4 Removable media mode transitions                                         |                  |

| 7.5 Status and Error posting                                                 |                  |

| 7.6 Security Mode Feature Set                                                |                  |

| 8 Command Descriptions                                                       |                  |

| 8.1 ACKNOWLEDGE MEDIA CHANGE                                                 | 57               |

| 8.2 BOOT - POST-BOOT                                                         |                  |

| 8.3 BOOT - PRE-BOOT                                                          |                  |

| 8.4 CHECK POWER MODE                                                         |                  |

| 8.5 DOOR LOCK                                                                |                  |

| 8.6 DOOR UNLOCK                                                              |                  |

| 8.7 DOWNLOAD MICROCODE                                                       |                  |

| 8.8 EXECUTE DEVICE DIAGNOSTIC                                                |                  |

| 8.9 FORMAT TRACK                                                             |                  |

| 8.10 IDENTIFY DEVICE                                                         |                  |

| 8.10.1 Word 0: General configuration                                         |                  |

| 8.10.2 Word 1: Number of cylinders                                           |                  |

| 8.10.3 Word 2: Reserved                                                      |                  |

| 8.10.4 Word 3: Number of logical heads                                       |                  |

| 8.10.5 Word 4: Vendor specific data                                          |                  |

| 8.10.6 Word 5: Vendor specific data                                          |                  |

| 8.10.7 Word 6: Number of logical sectors per logical track                   |                  |

| 8.10.8 Words 7-9: Vendor specific data                                       |                  |

| 8.10.9 Words 10-19: Serial Number                                            |                  |

| 8.10.10 Word 20: Vendor specific data.                                       |                  |

| 8.10.11 Word 21: Vendor specific data                                        |                  |

| 8.10.12 Word 22: Number of vendor specific bytes on READ/WRITE LONG commands | 70               |

| 8.10.13 Word 23-26: Firmware revision.                                       |                  |

| 8.10.14 Words 27-46: Model number                                            |                  |

| 8.10.15 Word 47: READ/WRITE MULTIPLE support                                 |                  |

| 8.10.16 Word 48: Reserved                                                    |                  |

| 8.10.17 Word 49: Capabilities                                                |                  |

| 8.10.17.1 IORDY Support                                                      |                  |

| 8.10.17.2 IORDY Can Be Disabled                                              |                  |

| 8.10.17.3 LBA supported                                                      |                  |

| 8.10.17.4 DMA supported                                                      |                  |

| 8.10.18 Word 50: Security Mode                                               |                  |

| 8.10.19 Word 51: PIO data transfer cycle timing mode                         |                  |

| 8.10.20 Word 52: Single Word DMA data transfer cycle timing mode             |                  |

| 8.10.21 Word 53: Field Validity                                              |                  |

| 8.10.22 Word 54: Number of current logical cylinders                         | 71               |

| 8.10.23 Word 55: Number of current logical heads                             |                  |

| 8.10.24 Word 56: Number of current logical sectors per logical track         |                  |

| 8.10.25 Word 57-58: Current capacity in sectors                              |                  |

| 8.10.26 Word 59: Multiple sector setting                                     | 72               |

| 8.10.27 Word 60-61: Total number of user addressable sectors                 | . <u>-</u><br>72 |

| 8.10.28 Word 62: Single word DMA transfer                                    |                  |

| 8.10.29 Word 63: Multiword DMA transfer                                      | . <u>-</u><br>72 |

| 8.10.30 Word 64: Flow Control PIO Transfer Modes Supported                   |                  |

| 8.10.31 Word 65: Minimum Multiword DMA Transfer Cycle Time Per Word   |     |

|-----------------------------------------------------------------------|-----|

| 8.10.32 Word 66: Manufacturer's Recommended Multiword DMA Cycle Time  |     |

| 8.10.33 Word 67: Minimum PIO Transfer Cycle Time Without Flow Control |     |

| 8.10.34 Word 68: Minimum PIO Transfer Cycle Time With IORDY           |     |

| 8.10.35 Words 69-70: Reserved for future PIO modes                    |     |

| 8.10.36 Words 71-127: Reserved                                        |     |

| 8.10.37 Words 128-159: Vendor specific                                | 73  |

| 8.10.38 Words 160-255: Reserved                                       | 73  |

| 8.11 IDENTIFY DEVICE DMA                                              | 74  |

| 8.12 IDLE 75                                                          |     |

| 8.13 IDLE IMMEDIATE                                                   |     |

| 8.14 INITIALIZE DEVICE PARAMETERS                                     |     |

| 8.15 MEDIA EJECT                                                      | 78  |

| 8.16 NOP 79                                                           |     |

| 8.17 READ BUFFER                                                      |     |

| 8.18 READ DMA (with retries and without retries)                      |     |

| 8.19 READ LONG (with retries and without retries)                     |     |

| 8.20 READ MULTIPLE                                                    |     |

| 8.21 READ SECTOR(S) (with retries and without retries)                |     |

| 8.22 READ VERIFY SECTOR(S) (with retries and without retries)         |     |

| 8.23 RECALIBRATE                                                      |     |

| 8.24 SECURE DISABLE                                                   |     |

| 8.25 SECURE ENABLE RO                                                 |     |

| 8.26 SECURE ENABLE RW                                                 |     |

| 8.27 SECURE ENABLE WP                                                 |     |

| 8.28 SECURE LOCK                                                      |     |

| 8.29 SECURE STATE                                                     |     |

| 8.30 SECURE UNLOCK                                                    | 93  |

| 8.31 SEEK 94<br>8.32 SET FEATURES                                     | 0.5 |

|                                                                       |     |

| 8.33 SET MULTIPLE MODE                                                | 9/  |

| 8.34 SLEEP98<br>8.35 STANDBY                                          | 00  |

| 8.36 STANDBY IMMEDIATE                                                |     |

| 8.37 WRITE BUFFER                                                     |     |

| 8.38 WRITE DMA (with retries and without retries)                     |     |

| 8.39 WRITE LONG (with retries and without retries)                    |     |

| 8.40 WRITE MULTIPLE                                                   |     |

| 8.41 WRITE SAME                                                       |     |

| 8.42 WRITE SECTOR(S) (with retries and without retries)               |     |

| 8.43 WRITE VERIFY                                                     |     |

| 9 Protocol.                                                           |     |

| 9.1 Power on and hardware resets.                                     |     |

| 9.1.1 Power on and hardware resets - device 0                         |     |

| 9.1.2 Power on and hardware resets - device 1                         |     |

| 9.2 Software reset                                                    |     |

| 9.2.1 Software reset - device 0                                       |     |

| 9.2.2 Software reset - device 1                                       |     |

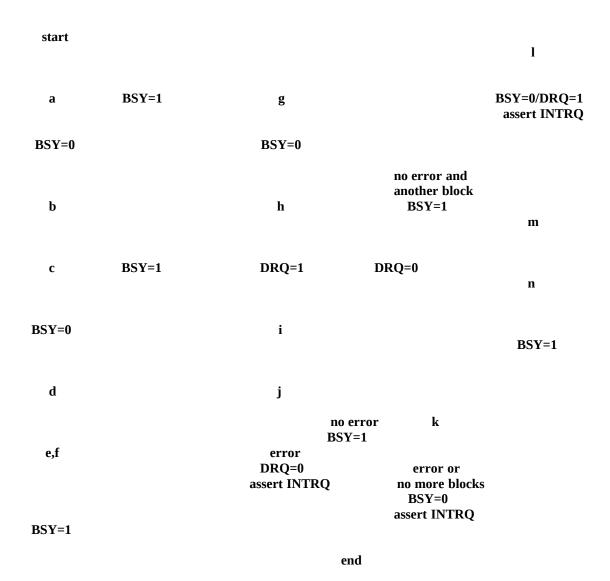

| 9.3 PIO data in commands                                              |     |

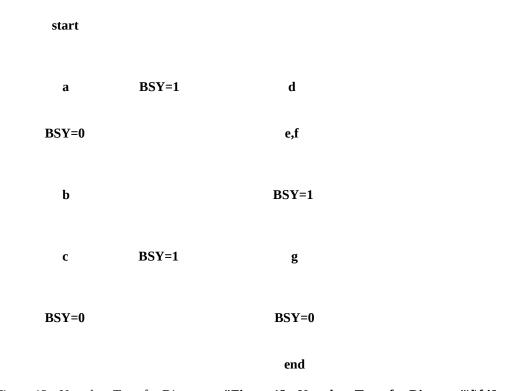

| 9.4 PIO data out commands                                             |     |

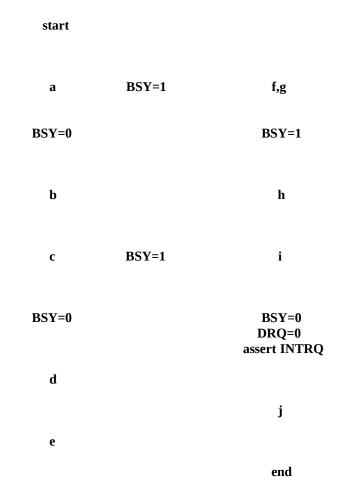

| 9.5 Non-data commands                                                 |     |

| 9.6 DMA data transfer commands (optional)                             |     |

| 9.7 Device 0 only configurations                                      |     |

| 9.8 Device 1 only configurations                                      |     |

| 10 Timing                                                             |     |

| 10.1 Deskewing                                                        |     |

| 10.2 Symbols                                                          |     |

| 10.3 Terms 122                                                        |     |

| 10.4 Bit Setting=0                                                             |     |

|--------------------------------------------------------------------------------|-----|

| 10.5 Data Transfers                                                            |     |

| 10.5.1 PIO Data Transfers                                                      |     |

| 10.5.2 Single Word DMA Data Transfer                                           | 126 |

| 10.5.3 Multiword DMA Data Transfer                                             |     |

| 10.6 Power on and hard reset                                                   |     |

| Annex A. Diagnostic and reset considerations from a device firmware standpoint | 131 |

| A.1 Power on and hardware reset (RESET-)                                       | 131 |

| A.2 Software reset                                                             |     |

| A.3 Device diagnostic command                                                  | 131 |

| A.4 Truth table                                                                | 131 |

| A.5 Power on or hardware reset algorithm                                       | 131 |

| A.5.1 Algorithm for Device 0                                                   |     |

| A.5.2 Algorithm for Device 1                                                   | 132 |

| A.6 Software Reset Algorithm                                                   | 133 |

| A.6.1 Algorithm for Device 0                                                   | 133 |

| A.6.2 Algorithm for Device 1                                                   |     |

| A.7 Diagnostic Command Algorithm                                               | 134 |

| A.7.1 Algorithm for Device 0                                                   |     |

| A.7.2 Algorithm for Device 1                                                   | 134 |

| Annex B. 44-Pin Small Form Factor Connector                                    |     |

| B.1 44-pin signal assignments                                                  | 136 |

| Annex C. 68-Pin Small Form Factor Connector                                    | 138 |

| C.1 Overview                                                                   |     |

| C.2 Signals                                                                    | 138 |

| C.3 Signal Descriptions                                                        | 138 |

| C.3.1 CD1- (Card Detect 1)                                                     | 140 |

| C.3.2 CD2- (Card Detect 2)                                                     | 140 |

| C.3.3 CS1- (Device chip Select 1)                                              | 140 |

| C.3.4 DMACK- (DMA Acknowledge)                                                 |     |

| C.3.5 DMARQ (DMA Request)                                                      | 140 |

| C.3.6 IORDY (I/O Channel Ready)                                                | 140 |

| C.3.7 M/S- (Master/Slave)                                                      |     |

| C.3.8 SELATA- (Select 68-pin ATA)                                              | 140 |

| C.4 Removability Considerations                                                |     |

| C.4.1 Device Recommendations                                                   | 141 |

| C.4.2 Host Recommendations                                                     | 141 |

| Annex D. Identify Device Data For ATA Devices Below 8 GB                       |     |

| D.1 Definitions and Background Information                                     |     |

| D.2 Cylinder, Head and Sector Addressing                                       |     |

| D.2.1 Word 1                                                                   | 143 |

| D.2.2 Word 3                                                                   | 143 |

| D.2.3 Word 6                                                                   |     |

| D.2.4 Use of words 53 through 58                                               | 143 |

| D.2.5 Word 53                                                                  | 143 |

| D.2.6 Word 54                                                                  | 144 |

| D.2.7 Word 55                                                                  | 144 |

| D.2.8 Word 56                                                                  | 144 |

| D.2.9 Words 57-58                                                              |     |

| D.3 Logical Block Addressing                                                   | 144 |

| D.3.1 Words 60-61                                                              | 144 |

| D.3.2 Orphan Sectors                                                           |     |

| Annex E. ATA Command Set Summary                                               | 145 |

| Figures                                                         |     |

|-----------------------------------------------------------------|-----|

| μFigure 1 - ATA Interface Cabling Diagram                       | 17  |

| Figure 2 - Drive Side Connector Pin Numbering                   |     |

| Figure 3 - 40-Pin Connector Mounting                            | 19  |

| Figure 4 - Cable Select Example                                 | 27  |

| Figure 5 - Power Management Modes                               | 46  |

| Figure 6 - Removable Modes                                      | 48  |

| Figure 7 - BSY and DRDY timing for Diagnostic command           | 65  |

| Figure 8 - BSY and DRDY timing for power on and hardware resets | 109 |

| Figure 9 - BSY and DRDY timing for software reset               | 110 |

| Figure 10 - PIO Data Transfer Diagram                           |     |

| Figure 11 - PIO Data Transfer Out Diagram                       | 115 |

| Figure 12 - Non-data Transfer Diagram                           | 117 |

| Figure 13 - DMA Data Transfer Diagram                           | 119 |

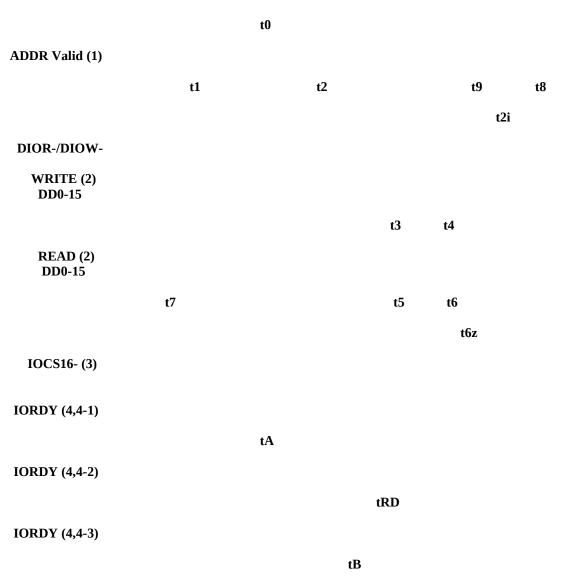

| Figure 14 - PIO Data Transfer to/from Device                    | 124 |

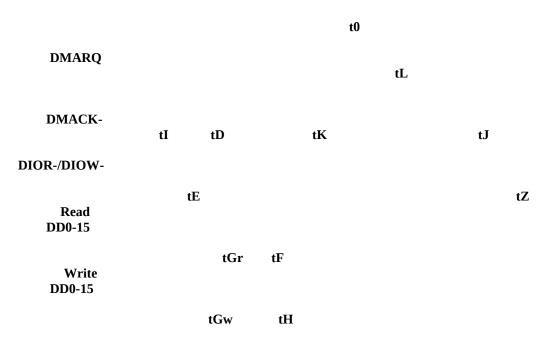

| Figure 15 - Single Word DMA Data Transfer                       |     |

| Figure 16 - Multiword DMA Data Transfers                        |     |

| Figure 17 - Reset Sequence                                      |     |

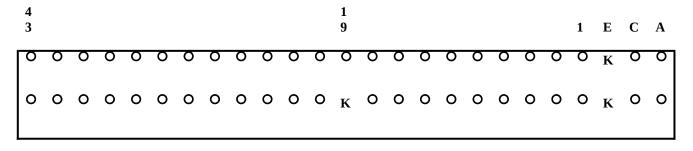

| Figure 18 - 44-pin Connector                                    | 136 |

|                                                                 |     |

| Tables<br>μTable 1 - Byte Order - 16 bit transfer               | 15  |

| Table 2 - Byte Order - 8 bit transfers                          |     |

| Table 3 - DC Interface Using 4 Pin Power Connector              |     |

| Table 4 - DC Characteristics                                    |     |

| Table 5 - AC Characteristics                                    |     |

| Table 6 - ATA-2 Driver Types and Required Pull-ups              |     |

| Table 7 - Interface Signal Names and Pin Assignments            |     |

| Table 8 - Interface Signals - Alphabetical Listing              |     |

| Table 9 - I/O Port Functions and Selection Addresses            |     |

| Table 10 - Power Conditions                                     |     |

| Table 11 - Status and Error Usage                               |     |

| Table 12 - Command Codes and Parameters                         |     |

| Table 13 - Diagnostic Codes                                     |     |

| Table 14 - Identify Device Information                          |     |

| Table 15 - Automatic Idle Timer Periods                         |     |

| Table 16 - Security Mode State                                  |     |

| Table 17 - Set Features Register Definitions                    |     |

| Table 18 - Transfer/Mode Values                                 |     |

| Table 19 - Automatic Standby Timer Periods                      |     |

| Table 20 - PIO Data Transfer to/from Device                     |     |

| Table 21 - Single Word DMA Data Transfer                        |     |

| Table 22 - Multiword DMA Data Transfer                          |     |

| Table 23 - Reset Sequence                                       |     |

| Table 24 - Reset Error Register Values                          |     |

| Table 25 - Signal Assignments for 44-pin ATA                    |     |

| Table 26 - Signal Assignments for 68-pin ATA                    |     |

| Table 27 - Word 3 Value                                         |     |

| Table 28 - Command Matrix                                       |     |

| Table 29 - Commands Sorted By Command Value                     |     |

#### **Foreword**

This standard replaces X3.\*\*\*-199x, the AT Attachment Interface with Extensions standard.

This standard encompasses the following:

Clause 1 describes the scope.

Clause 2 lists the normative references.

Clause 3 provides definitions, abbreviations and conventions used within this document.

Clause 4 contains the electrical and mechanical characteristics; covering the interface cabling requirements of the DC, data cables and connectors.

Clause 5 contains the signal descriptions of the AT Attachment Interface.

Clause 6 contains descriptions of the registers of the AT Attachment Interface.

Clause 7 describes the general operating requirements of the AT Attachment Interface.

Clause 8 contains descriptions of the commands of the AT Attachment Interface.

Clause 9 contains an overview of the protocol of the AT Attachment Interface.

Clause 10 contains the interface timing diagrams.

Annexes A through E are informative.

### Introduction

When the first IBM PC™ (Personal Computer) was introduced, there was no hard disk storage capability. Successive generations of product resulted in the inclusion of a hard disk as the primary storage device. When the PC AT™ was developed, a hard disk was the key to system performance, and the controller interface became a de facto industry interface for the inclusion of hard disks in PC ATs.

The price of desktop systems has declined rapidly because of the degree of integration which reduced the number of components and interconnects. A natural outgrowth of this integration was the inclusion of controller functionality into the hard disk.

In October 1988 a number of device suppliers formed the Common Access Method Committee to encourage an industry-wide effort to adopt a common software interface to dispatch input/output requests to SCSI devices. Although this was the primary objective, a secondary goal was to specify what was known as the AT Attachment interface. The resulting AT Attachment Interface For Disk Drives standard fulfilled that requirement.

As personal computer type systems continued to evolved, there was a need to extend the capabilities of the interface. The lap-top and small computer systems needed to modify the mechanical aspects of the interface. High performance systems needed to have enhanced transfer rates. In addition, there were a number of issues in the AT Attachment standard that needed to be addressed. These initial issues resulted in the AT Attachment Interface with Extensions.

Still further evolution has necessitated the developement of the AT Attachment-3 interface standard.

### 1 Scope

This standard replaces the AT Attachment Interface with Extensions standard, X3.\*\*\*-199x. This standard extends the AT Attachment Interface with the addition of new commands, and defining new functions. In addition, general improvements have been made in content for completeness and to improve clarity.

This standard defines the AT Attachment Interface. This standard defines an integrated interfaces between devices and host processors. It provides a common point of attachment for systems manufacturers, system integrators, and suppliers of intelligent devices.

The application environment for the AT Attachment Interface is any device which uses internal storage.

The PC AT Bus<sup>™</sup> is a widely used and implemented interface for which a variety of devices have been manufactured. As a means of reducing size and cost, a class of products has emerged which embed the controller functionality in the device. Because of their compatibility with existing AT hardware and software this interface quickly became a de facto industry standard. While the AT Attachment Interface has its roots in the PC AT Bus<sup>™</sup>, its use has extended to many other systems.

### 2 Normative references

The AT Attachment Interface for Disk Drives, X3.221-1994. The AT Attachment Interface with Extensions, X3.\*\*\*-199x.

### 3 Definitions, abbreviations and conventions

### 3.1 Definitions and Abbreviations

For the purposes of this International Standard, the following definitions apply.

ATA (AT attachment) - ATA defines the physical, electrical, transport, and command protocols for the internal attachment of block storage devices.

AWG - American Wire Gauge.

Command acceptance - A command is considered accepted whenever the host writes to the Command Register and the device currently selected has its BSY bit equal to zero. An exception exists for the EXECUTE DIAGNOSTIC command (see Clause ).

CHS (Cylinder-head-sector) - This term defines the addressing of the device as being by cylinder number, head number and sector number.

Data block - This term describes a unit of data words transferred using PIO data transfer. A data block is transferred between the host and the device as a complete unit. A data block is a sector, except for data blocks of a READ MULTIPLE, WRITE MULTIPLE, READ LONG and WRITE LONG commands. In the cases of READ MULTIPLE and WRITE MULTIPLE commands, the size of the data block may be changed in multiples of sectors by the SET MULTIPLE MODE command. In the cases of READ LONG and WRITE LONG, the size of the data block is a sector plus a vendor specific number of bytes. The default length of the vendor specific bytes associate with the READ LONG and WRITE LONG commands is four bytes, but may be changed by use of the SET FEATURES command.

Device - Device is a storage peripheral. Traditionally, a device on the ATA interface has been a hard disk drive, but any form of storage device may be placed on the ATA interface provided it adheres to this standard.

Device selection - A device is selected when the DEV bit of the Drive/Head register is equal to the device number assigned to the device by means of a Device 0/Device 1 jumper or switch, or use of the CSEL signal.

DMA (Direct memory access) - A means of data transfer between device and host memory without processor intervention.

LBA (Logical block addess) - This term defines the addressing of the device as being by the linear mapping of sectors.

Master - Previous to this standard, Device 0 has also been referred to as the master. Through out this document the term Device 0 shall be used.

Optional - This term describes features which are not required by the standard. However, if any optional feature defined by the standard is implemented, it shall be done in the way defined by the standard. Describing a feature as optional in the text is done to assist the reader.

PIO (Programmed input/output) - A means of accessing device registers. PIO is also used to describe one form of data transfers. PIO data transfers are performed by the host processor utilizing PIO register accesses to the Data register.

Reserved - Reserved bits, bytes, words, fields and code values are set aside for future standardization. Their use and interpretation may be specified by future extensions to this or other standards. A reserved bit, byte, word or field shall be set to zero, or in accordance with a future extension to this standard. The recipient shall not check reserved bits, bytes, words or fields. Receipt of reserved code values in defined fields shall be treated as an error.

Sector - A uniquely addressable set of 256 words (512 bytes).

Slave - Previous to this standard, Device 1 has also been referred to as the slave. Through out this document the term Device 1 shall be used.

Unrecoverable error - An unrecoverable error is defined as having occurred at any point when the device sets either the ERR bit or the DF bit to one and the BSY bit to zero in the Status register when processing of a command.

VA (Vendor specific) - This term is used to describe bits, bytes, fields and code values which are reserved for vendor specific purposes. These bits, bytes, fields and code values are not described in this standard, and may be used in a way that varies between vendors. This term is also applied to levels of functionality whose definition is left to the vendor.

#### 3.2 Conventions

If there is a conflict between text and tables, the table shall be accepted as being correct.

# 3.2.1 Keywords

Lower case is used for words having the normal English meaning. Certain words and terms used in this International Standard have a specific meaning beyond the normal English meaning. These words and terms are defined either in Clause or in the text where they first appear.

The names of abbreviations, commands, fields, and acronyms used as signal names are in all uppercase (e.g.,

IDENTIFY DEVICE). Fields containing only one bit are usually referred to as the "name" bit instead of the "name" field. (See Clause for the naming convention used for naming bits.)

Names of device registers begin with a capital letter (e.g., Cylinder Low register).

### 3.2.2 Numbering

Numbers that are not immediately followed by a lower-case "b" or "h" are decimal values. Numbers that are immediately followed by a lower-case "b" (e.g., 01b) are binary values. Numbers that are immediately followed by a lower-case "h" (e.g., 3Ah) are hexadecimal values.

### 3.2.3 Signal Conventions

Signal names are shown in all upper case letters.

All signals are either high active or low active signals. A dash character (-) at the end of a signal name indicates it is a low active signal. A low active signal is true when it is below ViL, and is false when it is above ViH. No dash at the end of a signal name indicates it is a high active signal. A high active signal is true when it is above ViH, and is false when it is below ViL.

Asserted means that the signal is driven by an active circuit to its true state.

Negated means that the signal is driven by an active circuit to its false state.

Released means that the signal is not actively driven to any state. Some signals have bias circuitry that pull the signal to either a true state or false state when no signal driver is actively asserting or negating the signal. These cases are noted under the description of the signal, and their released state is stated.

Control signals that may be used for two mutually exclusive functions are identified with their two names separated by a colon e.g. SPSYNC:CSEL can be used for either the Spindle Sync (SPSYNC) or the Cable Select (CSEL) functions.

### 3.2.4 Bit Conventions

Bit names are shown in all upper case letters except where a lower case n precedes a bit name. If there is no preceding n, then when BIT is equal to one the meaning of the bit is true, and when BIT is equal to zero the meaning of the bit is false. If there is a preceding n, then when nBIT is equal to zero the meaning of the bit is true and when nBIT is equal to one the meaning of the bit is false.

# 3.2.5 Byte Ordering For 8-bit and 16-bit Data Transfers

Assuming a block of data contains "n" bytes of information, and the bytes are labeled Byte(0) through Byte(n-1), where Byte(0) is first byte of the field, and Byte(n-1) is the last byte of the block.

When such a block of data is transferred on the ATA interface in 16 bit wide transfer mode, the bytes shall be presented as shown in Table 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr'' \l\f t\setminus 1 - Byte Order - 16 bit transferr''

Table 1 - Byte Order - 16 bit transfertc "Table 1 - Byte Order - 16 bit transfer"\\\f t\\\f\$

| DD |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| First transfer  | sfer Byte (1) |            |  | Byte (0) |            |  |  |  |  |  |  |  |  |  |  |

|-----------------|---------------|------------|--|----------|------------|--|--|--|--|--|--|--|--|--|--|

| Second transfer |               | Byte (3)   |  |          | Byte (2)   |  |  |  |  |  |  |  |  |  |  |

|                 |               |            |  |          |            |  |  |  |  |  |  |  |  |  |  |

| Last transfer   |               | Byte (n-1) |  |          | Byte (n-2) |  |  |  |  |  |  |  |  |  |  |

When such a block of data is transferred on the ATA interface in 8 bit wide transfer mode, the bytes shall be presented in Table 2 - Byte Order - 8 bit transfert "Table 2 - Byte Order - 8 bit transfers"  $1 \pm 8$

Table 2 - Byte Order - 8 bit transfertc "Table 2 - Byte Order - 8 bit transfers"\l\f t\\$

| Table 2 - Byte Order - 6 bi | DD | DD | DD | DD   | DD     | DD | DD | DD |

|-----------------------------|----|----|----|------|--------|----|----|----|

|                             | 7  | 6  | 5  | 4    | 3      | 2  | 1  | 0  |

|                             |    |    |    |      |        |    |    |    |

| First transfer              |    |    |    | Byte | e (0)  |    |    |    |

|                             |    |    |    |      |        |    |    |    |

| Second transfer             |    |    |    | Byte | e (1)  |    |    |    |

|                             |    |    |    |      |        |    |    |    |

| ******                      |    |    |    |      |        |    |    |    |

|                             |    |    |    |      |        |    |    |    |

| Next to last transfer       |    |    |    | Ryto | (n-2)  |    |    |    |

| ivext to last transfer      |    |    |    | Буце | (11-2) |    |    |    |

|                             |    |    |    |      |        |    |    |    |

| Last transfer               |    |    |    | Byte | (n-1)  |    |    |    |

|                             |    |    |    |      |        |    |    |    |

Note: The above description is for data on the ATA Interface. Host systems and/or host adapters may cause the order of data, as seen in the memory of the host, to be different.

### 4 Interface Physical and Electrical Requirements

The traditional 40-pin ATA interface is documented in this section as one of the connection schemes being utilized. Annex B and Annex C provide a basic definition of two alternative connection schemes.

### 4.1 Configuration

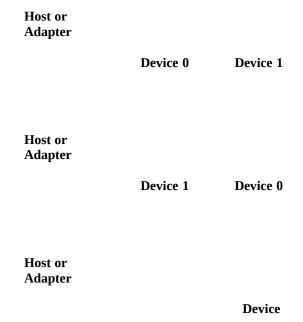

This standard defines the ATA interface containing a single host or host adapter and one or two devices. If two devices are connected to the interface, they are connected in a daisy chained configuration. One device is configured as Device 0 and the other device as Device 1.

The designation of a device as Device 0 or Device 1 may be made in a number of ways:

- · a switch or a jumper on the device

- use of the Cable Select (CSEL) pin

In a two drive configuration, the order of placement of Device 0 and Device 1 on the ATA interface cable is not significant to the operation of the interface.

If only a single device is attached via the ATA interface to a host, it is recommended that the host and the device be placed at the two ends of the cable.

Also see Clause.

Figure 1- ATA Interface Cabling Diagram" \l\f i\f\ i\f\

# 4.2 **DC** cable and connector

The device receives DC power through a 4-pin connector.

# 4.2.1 **4-pin power**

The pin assignments are shown in Table 3 - DC Interface Using 4 Pin Power Connectortc "Table 3 - DC Interface Using 4 Pin Power Connector"\l\f t\s\. Recommended part numbers for the mating connector to 18 AWG cable are shown below, but compatible parts may be used.

Connector (4 pin) AMP 1-480424-0 or compatible

Contacts (loose piece) AMP 60619-4 or compatible

Contacts (strip) AMP 61117-4 or compatible

Table 3 - DC Interface Using 4 Pin Power Connectortc "Table 3 - DC Interface Using 4 Pin Power Connector"\l\f

| Power line designation | Pin Number |

|------------------------|------------|

|                        |            |

| +12 Volts              | 1          |

|                        |            |

| +12 Volt Return        | 2          |

|                        |            |

| +5 Volt Return         | 3          |

|                        |            |

| +5 Volts               | 4          |

|                        |            |

|                        |            |

Figure 2 - Drive Side Connector Pin Numberingtc "Figure 2 - Drive Side Connector Pin Numbering"\\f

#### 4.3 I/O connector

The I/O connector is a 40-pin connector as shown in , with pin assignments as shown in Table 7 - Interface Signal Names and Pin Assignmentstc "Table 7 - Interface Signal Names and Pin Assignments" \\forall t\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\right\ri

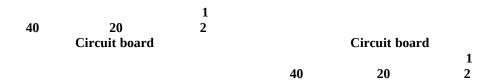

The pin locations are governed by the cable plug, not the receptacle. The way in which the receptacle is mounted on the printed circuit board affects the pin positions, and pin 1 should remain in the same relative position. This means the pin numbers of the receptacle may not reflect the conductor number of the plug. The header receptacle is not polarized, and all the signals are relative to pin 20, which is keyed.

By using the plug positions as primary, a straight cable can connect devices. As shown in , conductor 1 on pin 1 of the plug has to be in the same relative position no matter what the receptacle numbering looks like. If receptacle numbering was followed, the cable would have to twist 180 degrees between a device with top-mounted receptacles, and a device with bottom-mounted receptacles.

Figure 3 - 40-Pin Connector Mountingtc "Figure 3 - 40-Pin Connector Mounting"\\fi

Recommended part numbers for the mating connector are shown below, but equivalent parts may be used.

Connector (40 pin) 3M 3417-7000 or equivalent

Strain relief 3M 3448-2040 or equivalent

### 4.4 **I/O** cable

The cable specifications affect system integrity and the maximum length that can be supported in any application.

Flat cable (stranded 28 AWG) 3M 3365-40 or equivalent

Flat cable (stranded 28 AWG) 3M 3517-40 (shielded) or equivalent

Cable total length shall not exceed 0,46m (18 inches).

Cable capacitance shall not exceed 35 pf.

### 4.5 **Electrical Characteristics**

Interface signal are defined in Table 4 - DC Characteristicstc "Table 4 - DC Characteristics"\l\f t\s and Table 5 - AC Characteristicstc "Table 5 - AC Characteristics"\l\f t\s.

Table 4 - DC Characteristicstc "Table 4 - DC Characteristics"\l\f t\\$

|     | Description                          | Min        | Max        |

|-----|--------------------------------------|------------|------------|

| IoL | Driver sink current                  | 12mA       |            |

| IoH | Driver source current (1)            | 400uA      |            |

| Vih | Voltage Input High                   | 2,0 V d.C. |            |

| Vil | Voltage Input Low                    |            | 0,8 V D.C. |

| Voh | Voltage Output High (Ioh = -400 u A) | 2,4 V D.C. |            |

| Vol | Voltage Output Low (Iol = 12ma)      |            | 0,5 V D.C. |

#### Note:

(1) IoH value at 400 uA is insufficient in the case of DMARQ which is typically pulled low by a 5.6k ohm resistor.

Table 5 - AC Characteristicstc "Table 5 - AC Characteristics"\I\f t\}

|       | Description                                  | Min | Max   |

|-------|----------------------------------------------|-----|-------|

| tRISE | Rise time for any signal on AT interface (1) | 5ns |       |

| tFALL | Fall time for any signal on AT interface (1) | 5ns |       |

| Cin   | Input Capacitance (each host or Device)      |     | 25 pf |

| Cout  | Output Capacitance (each host or Device)     |     | 25 pf |

#### Note:

(1) tRISE and tFALL are measured from 10-90% of full signal amplitude with a total capacitive load of 100~pf.

# 4.5.1 ATA-2 Driver Types and Required Pull-ups

Table 6 - ATA-2 Driver Types and Required Pull-upstc "Table 6 - ATA-2 Driver Types and Required Pull-ups"\I\

f t§

|                | f t§                                                                    |                                                                                                                                                        |                                                                                                                                                                        |                                                                                                                |

|----------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Source         | Driver<br>Type (1)                                                      | Pull-up at<br>Host (2)                                                                                                                                 | Pull-up at<br>each Device<br>(2)                                                                                                                                       | Notes                                                                                                          |

| Host           | TP                                                                      |                                                                                                                                                        |                                                                                                                                                                        |                                                                                                                |

| Bidir          | TS                                                                      |                                                                                                                                                        |                                                                                                                                                                        |                                                                                                                |

| Device         | TS                                                                      | 5.6K PD                                                                                                                                                |                                                                                                                                                                        | (3)                                                                                                            |

| Host           | TS                                                                      |                                                                                                                                                        |                                                                                                                                                                        |                                                                                                                |

| Device         | TS                                                                      | 1.0K                                                                                                                                                   |                                                                                                                                                                        | (4)                                                                                                            |

| Host<br>Device | TS/OC                                                                   | Ground                                                                                                                                                 | 10K<br>VS                                                                                                                                                              | (5)<br>(6)<br>(7)                                                                                              |

| Host           | TP                                                                      |                                                                                                                                                        |                                                                                                                                                                        |                                                                                                                |

| Device         | TS                                                                      |                                                                                                                                                        |                                                                                                                                                                        |                                                                                                                |

| Device         | OC                                                                      | 1.0K                                                                                                                                                   |                                                                                                                                                                        |                                                                                                                |

| Host           | TP                                                                      |                                                                                                                                                        |                                                                                                                                                                        |                                                                                                                |

| Device         | TS                                                                      |                                                                                                                                                        | 10K                                                                                                                                                                    |                                                                                                                |

| Host           | TP                                                                      |                                                                                                                                                        |                                                                                                                                                                        |                                                                                                                |

| Device         | OC                                                                      |                                                                                                                                                        | 10K                                                                                                                                                                    | (5)                                                                                                            |

|                | Bidir  Device  Host Device  Host Device  Host  Device  Host  Host  Host | Host TP  Bidir TS  Device TS  Host TS  Host TS  Host TS  Device TS  Oevice TS  TOC  Host TP  Device TS  Device TS  TS  TOC  TOC  Host TP  TOC  Host TP | Host TP  Bidir TS  Device TS 5.6K PD  Host TS  Device TS 1.0K  Ground  TS  Device TS  Device TS  Host TP  Device TS  Device TS  TP  TO  TO  TO  TO  TO  TO  TO  TO  TO | Host TP Bidir TS Device TS 5.6K PD  Host TS  Device TS  Over TS  Device TS  TS  TS  TS  TS  TS  TS  TS  TS  TS |

### Notes:

<sup>(1)</sup> TS=Tri-State; OC=Open Collector; TP=Totem-Pole; PU=Pull-up; PD=Pull-down; VS=Vendor specific

<sup>(2)</sup> All resistor values are minimum (lowest) allowed.

<sup>(3)</sup> ATA-3 defines this line to be tri-stated whenever the device is not selected or is not executing a DMA data transfer. When enabled by DMA transfer, it shall be driven high and

low by the device.

- (4) This signal should only be enabled during DIOR/DIOW cycles to the selected device.

- (5) See signal descriptions for information on dual use of this signal.

- (6) When used as CSEL, Line is grounded at Host and 10K Pull-up is required at both devices.

- (7) When used as SPSYNC, application is vendor specific.

### 5 Interface Signal Assignments and Descriptions

### 5.1 Signal summary

Table 7 - Interface Signal Names and Pin Assignmentstc "Table 7 - Interface Signal Names and Pin Assignments"\

I\f t\seta

| Description     | Source      | Pin | Acronym |

|-----------------|-------------|-----|---------|

| Reset           | Host        | 1   | RESET-  |

| Ground          | n/a         | 2   | Ground  |

| Data bus bit 7  | Host/Device | 3   | DD7     |

| Data bus bit 8  | Host/Device | 4   | DD8     |

| Data bus bit 6  | Host/Device | 5   | DD6     |

| Data bus bit 9  | Host/Device | 6   | DD9     |

| Data bus bit 5  | Host/Device | 7   | DD5     |

| Data bus bit 10 | Host/Device | 8   | DD10    |

| Data bus bit 4  | Host/Device | 9   | DD4     |

| Data bus bit 11 | Host/Device | 10  | DD11    |

| Data bus bit 3  | Host/Device | 11  | DD3     |

| Data bus bit 12 | Host/Device | 12  | DD12    |

| Data bus bit 2  | Host/Device | 13  | DD2     |

|                              |             | 1  |             |

|------------------------------|-------------|----|-------------|

| Data bus bit 13              | Host/Device | 14 | DD13        |

| Data bus bit 1               | Host/Device | 15 | DD1         |

| Data bus bit 14              | Host/Device | 16 | DD14        |

| Data bus bit 0               | Host/Device | 17 | DD0         |

| Data bus bit 15              | Host/Device | 18 | DD15        |

| Ground                       | n/a         | 19 | Ground      |

| (keypin)                     | n/a         | 20 | Reserved    |

| DMA Request                  | Device      | 21 | DMARQ       |

| Ground                       | n/a         | 22 | Ground      |

| I/O Write                    | Host        | 23 | DIOW-       |

| Ground                       | n/a         | 24 | Ground      |

| I/O Read                     | Host        | 25 | DIOR-       |

| Ground                       | n/a         | 26 | Ground      |

| I/O Ready                    | Device      | 27 | IORDY       |

| Spindle Sync or Cable Select | (Note 1)    | 28 | SPSYNC:CSEL |

| DMA Acknowledge              | Host        | 29 | DMACK-      |

| Ground                       | n/a         | 30 | Ground      |

| Interrupt Request            | Device      | 31 | INTRQ       |

| 16 Bit I/O                   | Device      | 32 | IOCS16-     |

| Device Address Bit 1                      | Host | 33 | DA1    |

|-------------------------------------------|------|----|--------|

| Passed Diagnostics                        | (1)  | 34 | PDIAG- |

| Device Address Bit 0                      | Host | 35 | DA0    |

| Device Address Bit 2                      | Host | 36 | DA2    |

| Chip Select 0                             | Host | 37 | CS0-   |

| Chip`Select 1                             | Host | 38 | CS1-   |

| Device Active or Slave (Device 1) Present | (1)  | 39 | DASP-  |

| Ground                                    | n/a  | 40 | Ground |

Note:

<sup>(1)</sup> See signal descriptions for information on source of these signals

Table 8 - Interface signals - Alphabetical Listing $\mathbf{tc}$  "Table 8 - Interface Signals - Alphabetical Listing"\l\f

| Signal       Pin         CS0-       37         CS1-       38         DA0       35         DA1       33         DA2       36         DASP-       39         DD0       17         DD1       15         DD2       13         DD3       11         DD4       9         DD5       7         DD6       5         DD7       3         DD8       4         DD9       6         DD10       8 |       | t§ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|

| CS1- 38  DA0 35  DA1 33  DA2 36  DASP- 39  DD0 17  DD1 15  DD2 13  DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD7 3  DD8 4                                                                                                                                                                                                                                                                 |       |    |

| DA0 35  DA1 33  DA2 36  DASP- 39  DD0 17  DD1 15  DD2 13  DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                          | CS0-  | 37 |

| DA1 33  DA2 36  DASP- 39  DD0 17  DD1 15  DD2 13  DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                  | CS1-  | 38 |

| DA2 36  DASP- 39  DD0 17  DD1 15  DD2 13  DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                          | DA0   | 35 |

| DASP- 39  DD0 17  DD1 15  DD2 13  DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                                  | DA1   | 33 |

| DD0 17  DD1 15  DD2 13  DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                                            | DA2   | 36 |

| DD1 15  DD2 13  DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                                                    | DASP- | 39 |

| DD2 13  DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                                                            | DD0   | 17 |

| DD3 11  DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                                                                    | DD1   | 15 |

| DD4 9  DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                                                                            | DD2   | 13 |

| DD5 7  DD6 5  DD7 3  DD8 4  DD9 6                                                                                                                                                                                                                                                                                                                                                   | DD3   | 11 |

| DD6 5 DD7 3 DD8 4 DD9 6                                                                                                                                                                                                                                                                                                                                                             | DD4   | 9  |

| DD7 3 DD8 4 DD9 6                                                                                                                                                                                                                                                                                                                                                                   | DD5   | 7  |

| DD8 4  DD9 6                                                                                                                                                                                                                                                                                                                                                                        | DD6   | 5  |

| DD9 6                                                                                                                                                                                                                                                                                                                                                                               | DD7   | 3  |

|                                                                                                                                                                                                                                                                                                                                                                                     | DD8   | 4  |

| DD10 8                                                                                                                                                                                                                                                                                                                                                                              | DD9   | 6  |

|                                                                                                                                                                                                                                                                                                                                                                                     | DD10  | 8  |

| DD11 10                                                                                                                                                                                                                                                                                                                                                                             | DD11  | 10 |

| Signal  | Pin         |

|---------|-------------|

| DD12    | 12          |

| DD13    | 14          |

| DD14    | 16          |

| DD15    | 18          |

| DIOR-   | 25          |

| DIOW-   | 23          |

| DMACK-  | 29          |

| DMARQ   | 21          |

| INTRQ   | 31          |

| IOCS16- | 32          |

| IORDY   | 27          |

| PDIAG-  | 34          |

| RESET-  | 1           |

| SPSYNC  | 28          |

| CSEL    | 28          |

| keypin  | 20          |

| ground  | 2,19,22,24, |

|         | 26,30,40    |

### 5.2 Signal descriptions

# 5.2.1 **CS0- (CHIP SELECT 0)**

This is the chip select signal from the host used to select the Command Block Registers. See Table 9 - I/O Port Functions and Selection Addressest "Table 9 - I/O Port Functions and Selection Addresses" \\ \text{t}.

Note: This signal has also been known in the industry as CS1FX-.

# 5.2.2 **CS1- (CHIP SELECT 1)**

This is the chip select signal from the host used to select the Control Block Registers. See Table 9 - I/O Port Functions and Selection Addressest "Table 9 - I/O Port Functions and Selection Addresses" \\ \text{t}.

Note: This signal has also been known in the industry as CS3FX-.

# 5.2.3 DA2, DA1, and DA0 (DEVICE ADDRESS)

This is the 3-bit binary coded address asserted by the host to access a register or data port in the device. See Table 9 - I/O Port Functions and Selection Addresses: "Table 9 - I/O Port Functions and Selection Addresses: "If the table 9 - I/O Port Functions and Selection Addresses are selection Addresses." If the table 9 - I/O Port Functions and Selection Addresses are selection Addresses."

### 5.2.4 DASP- (Device active, device 1 present)

This is a time-multiplexed signal which indicates that a device is active, or that Device 1 is present. This signal shall be an open collector output and each device shall have a 10K ohm pull-up resistor.

During power on initialization or after RESET- is negated, DASP- shall be deasserted by both Device 0 and Device 1 within 1 msec, and then Device 1 shall assert DASP- within 400 msec to indicate that Device 1 is present.

Device 0 shall allow up to 450 msec for Device 1 to assert DASP-.

DASP- shall be negated following acceptance of a command by Device 1 or after 31 seconds, whichever comes first.

Any time after negation of DASP-, either device may assert DASP- to indicate that a device is active.

If the host connects to the DASP- signal for the illumination of an LED or for any other purpose, the host shall ensure that the signal level seen on the ATA interface for DASP- shall maintain Voh and Vol compatibility, given the Ioh and Iol requirements of the DASP- device drivers.

### 5.2.5 **DD0-DD15 (Device Data)**

This is an 8- or 16-bit bi-directional data interface between the host and the device. The lower 8 bits are used for 8-bit transfers e.g. registers, vendor specific bytes associated with the READ LONG and WRITE LONG commands and, if the device supports the Features register capability to enable 8-bit-only data transfers (see Clause).

# 5.2.6 DIOR- (Device I/O read)

This is the read strobe signal from the host. The falling edge of DIOR- enables data from a register or data port of the device onto the signals, DD0-DD7 or DD0-DD15. The rising edge of DIOR- latches data at the host and the host shall not act on the data until it is latched.

# 5.2.7 DIOW- (Device I/O write)

This is the Write strobe signal from the host. The rising edge of DIOW- latches data from the signals, DD0-DD7 or DD0-DD15, into a register or the data port of the device. The device shall not act on the data until it is latched.

# 5.2.8 DMACK- (DMA acknowledge) (Optional)

This signal shall be used by the host in response to DMARQ to initiate DMA transfers.

NOTE: This signal may be negated by the Host to suspend the DMA transfer in process. For Multi-Word DMA transfers, the Device may negate DMARQ within the tL specified time (refer to Error: Reference source not found) once DMACK- is asserted and reassert it again at a later time to resume the DMA operation. Alternatively, if the device is able to continue the transfer of data, the device may leave DMARQ asserted and wait for the host to reassert DMACK-.

### 5.2.9 DMARQ (DMA request) (Optional)

This signal, used for DMA data transfers between host and device, shall be asserted by the device when it is ready to transfer data to or from the host. The direction of data transfer is controlled by DIOR- and DIOW-. This signal is used in a handshake manner with DMACK- i.e. the device shall wait until the host asserts DMACK- before negating DMARQ, and re-asserting DMARQ if there is more data to transfer.

This line shall be released (high impedance state) whenever the device is not selected or is selected and no DMA command is in progress. When enabled by DMA transfer, it shall be driven high and low by the device.

When a DMA operation is enabled, IOCS16-, CS0- and CS1- shall not be asserted and transfers shall be 16-bits wide.

NOTE: In ATA-1 devices, this signal was either totem-pole or tri-state in different implementations. In EISA systems, 5.6K pull-down is used to cause a logic low on undriven lines. ATA-2 defines this line to be in high-impedance mode except when DMA transfer is active from the selected device.

In systems which may use mixed devices where totem-pole drivers are used, and the system shares this line with other non-ATA devices, the ATA host or ATA adapter shall ensure that appropriate protection is employed to protect ATA device DMARQ drivers from damage.

# 5.2.10 **INTRQ (Device interrupt)**

This signal is used to interrupt the host system. INTRQ is asserted only when the device has a pending interrupt, the device is selected, and the host has cleared the nIEN bit in the Device Control register. If the nIEN bit is equal to one, or the device is not selected, this output is in a high impedance state, regardless of the presence or absence of a pending interrupt.

The interrupt pending condition shall be cleared by:

- · assertion of RESET- or

- · the setting of the SRST bit of the Device Control register, or

- · the host writing the Command register or

- the host reading the Status register

On PIO transfers, INTRQ is asserted at the beginning of each data block to be transferred. A data block is typically a single sector, except when declared otherwise by use of the SET MULTIPLE MODE command. An exception occurs on FORMAT TRACK, WRITE SECTOR(S), WRITE BUFFER and WRITE LONG commands - INTRQ shall not be asserted at the beginning of the first data block to be transferred.

On DMA transfers, INTRQ is asserted only once, after the command has completed.

If the system shares this line with non-ATA devices, the ATA host or ATA adapter shall ensure that appropriate protection is employed to protect ATA device INTRQ drivers from damage.

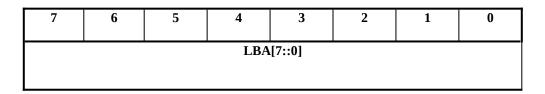

# 5.2.11 **IOCS16- (Device 16-bit I/O)**